# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS 2.0

# 2015 Edition

# EXECUTIVE REPORT

THE ITRS 2.0 IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

# The ITRS is Jointly Sponsored by

European Semiconductor Industry Association

Japan Electronics and Information Technology Industries Association

Korea Semiconductor Industry Association

Taiwan Semiconductor Industry Association

Semiconductor Industry Association

# 2015 ITRS 2.0 ACKNOWLEDGMENTS

INTERNATIONAL ROADMAP COMMITTEE *Europe*—Mart Graef, Bert Huizing, Reinhard Mahnkopf *Japan*— Hidemi Ishiuchi, Yoshihiro Hayashi, Nobuyuki Ikumi, Hiroyuki Miyakawa *Korea*—Siyoung Choi, Jae Hoon Choi, *Taiwan*—Sam Pam, Wilman Tsai *U.S.A.*—Paolo Gargini, Taffy Kingscott, Linda Wilson

#### **TECHNOLOGY WORKING GROUP KEY CONTRIBUTORS**

2015 Cross TWG Study Group (Technology Pacing)—Alan Allan, Dave Armstrong, An Chen, Mustafa Badaroglu, Joel Barnett, Roger Barth, Herbert Bennett, Bill Bottoms, Juan-antonio Carballo, Carlos Diaz, Alain Diebold, Paul Feeney, Mike Gaitan, Paolo Gargini, Mike Garner, Hidemi Ishiuchi, Dan Herr, Hirofumi Inoue, Scott Jones, Andrew Kahng, Leo Kenny, Rich Liu, Jürgen Lorenz, Steve Moffat, James Moyne, Mark Neisser, Kwok Ng, George Orji, Lothar Pfitzner, Gopal Rao, Thomas Skotnicki, Hitoshi Wakabayashi, Mike Walden, Linda Wilson, Osamu [Sam] Yamazaki, Victor Zhirnov, Paul Zimmerman

2015 Cross TWG Study Group (More than Moore)—Herbert Bennett, Bill Bottoms, Michel Brillouët, Juan-Antonio Carballo, Patrick Cogez, Erik DeBenedictis, Michael Gaitan, Mart Graef, Bert Huizing, Andrew Kahng, Reinhard Mahnkopf, Grace O' Malley, Chuck Richardson

System Integration—Juan-Antonio Carballo, Wei-Ting Jonas Chan, Andrew B. Kahng, Masaru Kakimoto, Siddhartha Nath, Toshitada Saito, Kenshu Seto, Gary Smith, Ichiro Yamamoto

Equipment—Kenichi Anzou, Test and Test Dave Armstrong, John Aslanian, Roger Barth, Yi Cai, Krishnendu Chakrabarty, Tapan Chakraborty, Sreejit Chakravarty, Wendy Chen, William Chui, Steve Comen, Zoe Conroy, Adam Cron, Al Crouch, Ted Eaton, Stefan Eichenberger, Bill Eklow, Paul Emmett, Ira Feldman, Francois-Fabien Ferhani, Shawn Fetterolf, Paul Franzon, Piergiorgio Galletta, Anne Gattiker, Sandeep Goel. Kazumi Hatayama, Hirokazu Hirayama, Hisao Horibe, Shuichi Ito, Hongshin Jun, Masahiro Kanase, Rohit Kapur, Toshiaki Kato, Brion Keller, Ajay Khoche, Satoru Kitagawa, Marc Knox, Masashi Kondo, Ken Lanier, Lenny Leon, Marc Loranger, Anthony Lum, Erik Jan Marinissen, Peter Maxwell, Cedric Mayor, Teresa McLaurin, Milanjan Mukherjee, Naoaki Narumi, Takeshi Nagasaka, Masaaki Namba, Phil Nigh, Akitoshi Nishimura, Hermann Obermeir, Jayson Park, Mike Peng-Li, Frank Poehl, Chris Portelli-Hale, Bill Price, Jeff Rearick, Herb Reiter, Mike Ricchetti, Michael Rodgers, Mark Roos, Tomonori Sasaki, Keno Sato, Masayuki Sato, Yasuo Sato, Ryuji Shimizu, Yoichi Shimizu, Fumio Sonoda, Hiroyoshi Suzuki, Tetsuo Tada, Satoru Takeda, Steven Tilden, Erik Volkerink, Adam Wright, Yervant Zorian

Integration. Devices. and Structures—Yasushi Akasaka, Hiroaki Ammo. Dimitri Antoniadis. Process Mustafa Badaroglu, Gennadi Bersuker, Azeez Bhavnagarwala, Frederic Boeuf, Alex Burenkov, Chorng-Ping Chang, Kin (Charles) Cheung, Kristin DeMeyer, James Fonseca, Yuzo Fukuzaki, Bill Gallagher, Christopher Henderson, Digh Hisamoto, Herve Jaouen, Gaspard Hiblot, Toshiro Hiramoto, Jim Hutchby, Jiro Ida, Hirofumi Inoue, Kunihiko Iwamoro, Moon-Young Jeong, Malgorzata Jurczak, Naoki Kasai, SungGeun Kim, Gerhard Klimeck, Fred Kuper, Hajime Kurata, Chung Lam, Robert Lander, Rich Liu, Witek Maszara, Toru Mogami, Kwok Ng, Tak Ning, Masaaki Niwa, Tony Oates, Hidekazu Oda, Sang Hyun Oh, Tatsuya Ohguro, Sam Pan, Jongwoo Park, Thierry Poiroux, Siddharth Potbhare, Kirk Prall, Xiang Qi, Mehdi Salmani-Jelodar, Thomas Schulz, Saurabh Sinha, Thomas Skotnicki, James Stathis, Toshihiro Sugii, Shinichi Takagi, Akira Tanabe, Tetsu Tanaka, Cheng-Tzung Tsai, Wilman Tsai, Hitoshi Wakabayashi, Philip Wong, Yanzhong Xu, Geoffrey Yeap, Makoto Yoshimi, Scott Yu, Peter Zeitzoff

*Outside System Connectivity*—*RF & AMS*- Hiroaki Ammo, James Bateman, Herbert Bennett, Pascal Chevalier, Hassan Farooq, David Harame, Anthony Immorlica, Jay John, James Li, Peter Magnee, Tatsuya Ooguro, Mark Rocchi, Michael Schroter, Sorin Voinigescu, *Photonic Interconnects*- Hiroaki Ammo, Carlos Augusto, Keren Bergman, Frederic Boeuf, Bill Bottoms, Mark Brongersma, William Chen, Patrick Cogez, Jason Coder, Jennifer Dionne, Shanhui Fan, Michael Gaitan, C. Michael Garner, Dan Gorcea, Andrew B. Kahng, Ashok Kapoor, Lionel Kimerling, Ashok Krishnamoorthy, David A.B. Miller III, Dick Otte, Chuck Richardson, Bernard Sautreuil, Jelena Vuckovic, Jean-Baptiste David, Alexei Tchelnokov

Heterogeneous Components—Steve Bart, Raji Baskaran, Steve Briet, Asif Chowdhury, Alissa Fitzgerald, Koji Fukumoto, Michael Gaitan, Buzz Hardy, Brian Jamieson, Akihiro Koga, Ron Lawes, Karen Lightman, Pete Loeppert, Erik Jan Lous, Mary Ann Maher, Jianmin Miao, Takashi Mihara, Arthur Morris, Yasutaka Nakashiba., Goro Nakatani, Fumihiko Nakazawa, Rob O'Reilly, Mervi Paulasto-Kröckel, Sasha Revel, Philippe Robert, John Rychcik, Tetsu Tanaka, Steve Tilden, Hiroshi Toshiyoshi, Joost van Beek, Chris van Hoof, Randy Wagner, Marcie Weinstein

Research Devices—Hiro Akinaga, Fabien Alibart, Joerg Appenzeller, Tetsuya Asai, Yuji Awano, Emerging Manuel Bibes, George Bourianoff, Bill Bottoms, Rod Bowman, Michel Brillouet, Geoffrey Burr, John Carruthers, Ralph Cavin, Chorn-Ping Chang, An Chen, Christophe Chevallier, U-In Chung, Byung Jin Cho, Sung Woong Chung, Luigi Colombo, Shamik Das, Erik DeBenedictis, Simon Deleonibus, Tetsuo Endoh, Paul Franzon, Akira Fujiwara, Mike Garner, Chakku Goplan, Bogdan Govoreanu, Wilfried Haensch, Dan Hammerstrom, Tsuyoshi Hasegawa, Shigenori Hayashi, Dan Herr, Marc Heyns, Mutsuo Hidaka, Toshiro Hiramoto, Jim Hutchby, Adrian Ionescu, Kiyoshi Kawabata, Seiichiro Kawamura, Masashi Kawasaki, Alex Khitun, Antoine Khoueir, Suhwan Kim, Gwan-hyeob Koh, Hyoungjoon Kim, Young-Bae Kim, Atsuhiro Kinoshita, Dae-Hong Ko. Hiroshi Kotaki, Michael Kozicki, Ilya Krivorotov, Franz Kreupl, Mark Kryder, Zoran Krivokapic, Kee-Won Kwon, Jangeun Lee, Jung-Ho Lee, Chenhsin Lien, Yun Fook Liew, Tsu-Jae King Liu, Louise Lome, Wei Lu, T.P. Ma, Reinhard Mahnkopf, Matthew Marinella, Stefan Meskers, Rene Meyer, Yasuyuki Miyamoto, Hiroshi Mizuta, Kotaki Murali, Kwok Ng, Michael Niemier, Fumiyuki Nihei, Dmitri Nikonov, Kei Noda, Byung-Gook Park, Ferdinand Peper, Er-Xuan Ping, Yutaka Ohno, Frank Register, Heike Riel, Shriram Ramanathan, Yaw Obeng. Dave Roberts. Kaushik Rov. Sayeef Salahuddin, Yoshiaki Saito, Akihito Sawa, Shintaro Sato, Barry Schechtman, Frank Schwierz, Sadas Shankar, Takahiro Shinada, Masayuki Shirane, Kaushal Singh, Thomas Skotnicki, Satoshi Sugahara, Shin-ichi Takagi, Tsutomu Teduka, Ming-Jinn Tsai, Ken Uchida, Thomas Vogelsang, Yasuo Wada, Rainer Waser, Jeff Welser, Frans Widershoven, Philip Wong, Dirk Wouters, Kojiro Yagami, David Yeh, In-Seok Yeo, Hiroaki Yoda, In-K Yoo, Victor Zhirnov

Emerging Research Materials-Hiro Akinaga, Scott Anderson, Nobuo Aoi, Bernd Appelt, Koji Arita, Hidefumi Asano, Koyu Asai, Yuji Awano, Rama Ayothi, Agnès Barthélémy, Joel Barnett, Chris Bencher, Daniel-Camille Bensahel, Kris Bertness, Stacey Bent, Manuel Bibes, Idriss Blakey, Mikael Björk, Serge Blonkowski, Kirill Bolotin, Lars Bomholt, August Bosse, Bill Bottoms, Rod Bowman, Jennifer Braggin, Alex Bratkovski, Robert Bristol, Ahmed Busnaina, David. A. Cahill, Jeff Calvert, Bernie Capraro, Gustau Catalan, Ian Cayrefourcq, Alek Chen, An Chen, Xiangyu Chen, Zhihong Chen, Joy, Cheng, Toyohiro Chikyow, Byung Jin Cho, Luigi Colombo, Michael Current, Ralph Dammel, Shamik Das, Juan DePablo, Anton Devilliers, Geraud Dubois, Catherine Dubourdieu, Glenn Fredrickson, Nathan Fritz, Roman Gafiteanu, Martin Giles, C. Michael Garner, Emmanuel Giannelis, Valeriy Ginzburg, Michael Goldstein, Padma Gopolan, Andrew Grenville, Roel Gronheid, Wilfried Haensch, Cliff Henderson, Daniel Herr, Hiro Hibino, Marc Hillmyer, Toshiro Hiramoto, ChiaHua Ho, Sung Eun Hong, Phil Hustad, Jim Hutchby, Harold Hwang, Diane Hymes, Koji Inoue, Kohei Ito, Hatsuo Ishida, Taisuke Iwai, Ajey Jacob, David Jamieson, Ali Javey, Berry Jonker, Yeon Sik Jung, Andrew Kahng, Ted Kamins, Masashi Kawaski, Leo Kenny, Choong-Un Kim, Philip Kim, Sang Ouk Kim, Joseph Kopanski, Michael Kozicki, Mark Kryder, Sean King, Atsuhiro Kinoshita, Paul Kohl, Blanka Magyari-Kope, Victor Krivokapic, Mark Kryder, Yi-Sha Ku, Hiroshi Kumigashira, Nabil Laachi, Jang Ein Lee, Ming-Hsiu (Eric) Lee, Yao-Jen Lee, Yi Jun Lee, Francois Leonard, Harry Levinson, Chenhsin Lien, Liew Yun Fook, Lloyd Litt, Ratchana Limary, Guanyang Lin, Cong (Colin) Liu, Shawna Liff. Chi Chun Liu, Timothy E. Long, Arantxa Maestre-Caro, Blanka Magyari-Kope, Prashant Majhi, Jochen Mannhart, Matthew Marinella, Francois Martin, Jennifer McKenna, Fumihiro Matsukura, Nobuyuki Matsuzawa, Dan Millward, Subhasish Mitra, Yoshiyuki Miyamoto, Steve Moffatt, Parvaneh Mokarian, Daniel Moraru, Mick Morris, Daniel Murray, Azad Naeemi, Christophe Navarro, Boris Naydenov, C. Gomez-Navarro, Paul Nealey, Mark Neisser, Kwok Ng, Quoc Ngo, Yoshio Nishi, Kei Noda, Yaw Obeng, Chris Ober, Katsumi Ohmori, Yutaka Ohno, Laurent Pain, Tomás Palacios, Samuel Pan, Jason Parker, Er-Xuan Ping, Jed Pitera, Joel Plawsky, Enrico Prati, Moshe Preil, Steve Putna, Ramamoorthy Ramesh, Nachiket Raravikar, Ben Rathsack, Heike Riel, Dave Roberts, Ricardo Ruiz, Thomas Russell, Tadashi Sakai, Dan Sanders, Sayeed Salahuddin, Gurtej Sandhu, Krishna Saraswat, Chandra Sarma, Hideyuki Sasaki, Shintaro Sato, Akihito Sawa, Mizuki Sekiya, Sadasiyan Shankar, Matthew Shaw, Michael Sheehan, Takahiro Shinada, David Shykind, Michelle Simmons, Kaushal K. Singh, Bruce Smith, Tom Smith, Mark Somervell, Satofumi Souma, Naoyuki Sugiyama, Raja Swaminathan, Masahiro Takemura, Koki Tamura, Anna Tchikoulaeva, Serge Tedesco, Jim Thackeray, Raluca Tiron, Yoshihiro Todokoro, Yasuhide Tomioka, Luan Tran, Peter Trefonas, Jean-Marc Triscone, Wilman Tsai, Emanuel Tutuc, Ken Uchida, Yasuo Wada, Kang Wang, Ming-Jinn Tsai, Jeffrey Weinhold, Andrew Whittaker, C.P. Wong, H.S. Philip Wong, Karen Wooley, Dirk Wouters, Wen-Li Wu, Shigeru Yamada, Fu-Liang Yang, Linda He Yi, Hiroaki Yoda, Bin Yu, Todd Younkin, Victor Zhirnov, Paul Zimmerman, Alfred Zinn, Ehrenfried Zschech, Ajoy Zutshi

*Front End Processes*—John C. Arnold, Souvik Banerjee, Joel Barnett, Meredith Beebe, Skip Berry, Ian Brown, Jeff Butterbaugh, Luke Chang, Glenn Gale, Michael Goss, Chris Gottschalk, Aomar Halimaoui, Yukinobu Hikosaka, Chris Hobbs, Eric A. Joseph, Andreas Kadavanich, Sivananda Kanakasabapathy, Deoksin Kil, Simon Kirk, Martin Knotter, Yong-Sun Koh, Kaushik Kumar, Cathy Labelle, Yannick Le Tiec, Kee Jeung Lee, Wei-Yip Loh, Prashant Majhi, Kevin McLaughlin, Paul Mertens, Ichiro Mizushima, Dan Mocuta, Bich-Yen Nguyen, Jin-Goo Park, Jagdish Prasad, Srini Raghavan, Maud Rao, Abbas Rastegar, Rick Reidy, Stefan Schmitz, Akshey Sehgal, Wolfgang Sievert, Chris Sparks, Allan Upham, Steven Verhaverbeke, M. Watanabe, Richard Wise, Klaus Wolke

Chris Bencher, *Lithography*—Tsukasa Azuma, Tatsuo Chijimatsu, Brian Cha, Will Conley, Ralph Dammel, Greg Denbeaux, Anton deVilliers, Masavuki Endo, Nigel Farrar, Ted Fedvnyshyn, Heiko Feldmann, Emily Gallagher, C. Michael Garner, Reiner Garreis, Cesar Garza, TS Gau, Bob Gleason, Frank Goodwin, Roel Gronheid, Naova Havashi, Long He, Yoshiaki Ikuta, Rik Jonckeere, Hyungsang Joo, Franklin Kalk, Kunihiko Kasama, Patrick Kearney, Insung Kim, Sachiko Kobayashi, Christof Krautschik, Y.C. Ku, Keishiro Kurihara, Jongwook Kye, David Kyser, Greg McIntyre, Dan Millward, Matt Malloy, Michael Lercel, ChangMoon Lim, Shy-Jay Lin, Lloyd Litt, Pawitter Mangat, Hiroaki Morimoto, Venkat Nagaswami, Hideo Nakashima, Patrick Naulleau Mark Neisser, Katsumi Ohmori, Yasushi Okubo, Masahiko Okumura, Kazuya Ota, Laurent Pain, Eric Panning, Moshe Preil, Doug Resnick, Morty Rothschild, Yoshitake Shusuke, Mark Slezak, Osamu Suga, Kazuhiro Takahashi, Takao Tamura, Serge Tedesco, Raluca Tiron, Walt Trybula, Plamen Tzviatkov, Rick Uchida, Fumikatsu Uesawa, Mauro Vasconi, Keiji Wada, Phil Ware, John Wiesner, Jim Wiley, Grant Willson, Obert Wood, Stefan Wurm, Jiro Yamamoto, Tetsuo Yamaguchi, Pei-Yang Yan, Anthony Yen, JeongHo Yeo, John Zimmerman

*Interconnect*—Nobuo Aoi, Lucile Arnaud, Koji Ban, Hans-Joachim Barth, Eric Beyne, Boyan Boyanov, Jon Candelaria, Chung-Liang Chang, Hsien-Wei Chen, Wen-Chih Chiou, Gilheyun Choi, Jinn-P. Chu, Mike Corbett, Alexis Farcy, Paul Feeney, Takashi Hayakawa, Paul Ho, Cheng-Chieh Hsieh, Masayoshi Imai, Atsunobu Isobayashi, Raymond Jao, Shin-Puu Jeng, Morihiro Kada, Sibum Kim, Nobuyoshi Kobayashi, Kaushik Kumar, Noh-jung Kwak, Hyeon Deok Lee, Anderson Liu, James Lu, Toshiro Maekawa, David Maloney, Akira Matsumoto, Azad Naeemi, Mehul Naik, Tomoji Nakamura, Yuichi Nakao, Akira Ouchi, Sesh Ramaswami, Hideki Shibata, Michele Stucchi, Zsolt Tokei, Thomas Toms, Manabu Tsujimura, Kazuyoshi Ueno, Osamu Yamazaki, Paul Zimmerman

*Factory Integration*—Daniel Babbs, Jonathan Chang, Gino Crispieri, Peter Csatary, Mike Czerniak, Chih-Wei (David) Huang, Slava Libman, Les Marshall, Supika Mashoro, Rick McKee, Steve Moffatt, James Moyne, Andreas Neuber, Kevin Pate, Dave Roberts, Markus Pfeffer, Dan Stevens, Ines Thurner, Makoto Yamamoto

*Heterogeneous Integration*—Amit Agrawal, Bernd Appelt, Muhannad S. Bakir, Dale Becker, Steve Bezuk, W. R. Bottoms, Yi-jen Chan, William Chen, Dan Evans, Michel Garnier, Steve Greathouse, Tom Gregorich, Richard Grzybowski, George Harman, Mike Hung, Ph.D, John Hunt, Rong-Shen Lee, Li Li, Sebastian Liau, Weichung Lo, Debendra Mallik, Keith Newman, Gary Nicholls, John Osenbach, Richard F. Otte, Bob Pfahl, Gilles Poupon, Gamal Refai-Ahmed, Charles Richardson, Theresa Sze, Coen Tak, Kripesh Vaidyanathan, James Wilcox, Jie Xue,

*Environment, Safety, and Health*—Laurie Beau, Mario Chen, Paul Connor, Reed Content, Terry Francis, Mike Garner, F. M. Hsu, Tom Huang, Francesca Illuzzi, Deb Kaiser, Leo Kenny, Alan Knapp, S. J. Ko, Hsi-An Kwong, Chris Lee, Slava Libman, Joey Lu, Mary Majors, Supika Mashiro, Toshi Matsuda, Rick McKee, Steve Moffatt, James Moyne, Andreas Neuber, Alain Pardon, Srini Raghavan, Dave Speed, Masahiro Takemura, Steve Tisdale, Pete Trefonas, Nausikaa van Hoornick, Kurt Werner, Dan Wilcox, Walter Worth, Don Yeaman

Yield Enhancement-Scott Anderson, Sabrina Anger, Joel Barnett, Dwight Beal, David Blackford, Yannick Bordel, Jennifer Braggin. Richard Brulls. Marc Camezind. Jan Cavelaars, Hubert Chu, Mike Clarke. Robert Clark. Jeff Covington, John DeGenova, Gil Delgado, Charley Dobson, Arnaud Favre, Guiseppe Fazio, Francois Finck, Herve Fontaine, Dan Fuchs, Takashi Futatsuki, Guillaume Gallet, Astrid Gettel, Rick Godec, Milton Goldwin, Barry Gotlinsky, Mathias Haeuser, Asad Haider, Jeff Hanson, Teruyuki Hayashi, Christoph Hocke, Masahiko Ikeno, Francesca Illuzzi, Hans Jansen, Jost Kames, Barry Kennedy, Keith Kerwin, Suhas Ketkar, Y.J. Kim, Katsunobu Kitami, Kaoru Kondoh, Naoki Kotani, John Kurowski, Sumio Kuwabara, Bob Latimer, Ravi Laxman, Slava Libman, Rick Lindblom, Juergen Lobert, Rushikesh Matkar, Yasuhiko Matsumoto, Tim Miller, Fumio Mizuno, William Moore, Jens Mueller, Chris Muller, Hiroshi Nagaishi, Andreas Neuber, Kazuo Nishihagi, Andreas Nutsch, Jim Ohlsen, Kevin Pate, Dilip Patel, Ruben Pessina, Lothar Pfitzner, Larry Rabellino, Abbas Rastegar, Dieter Rathei, Rich Riley, David Roberts, Dan Rodier, Biswanath Roy, Philippe Rychen, Koichiro Saga, Hideyuki Sakaizawa, Tony Schleisman, Akshey Sehgal, Yoshimi Shiramizu, Drew Sinha, Jim Snow, Terry Stange, Isamu Sugiyama, Paul Tan, Yoshitaka Tatsumoto, Ines Thurner, Hiroshi Tomita, Takahiro Tsuchiya, Allan Upham, Gerald Weineck, Dan Wilcox, Hubert Winzig, Bernie Zerfas

*Metrology*—Carlos Beitia; Mark Berry; Benjamin Bunday; Umberto Celano; SooBok Chin; Hyun Mo Cho; Alain Diebold; Brendan Foran, Michael Gaitan; Michael Garner; Christina Hacker; Karey Holland Masahiko Ikeno Yun Jung Jee; Eiichi Kawamura; Adrain Kiermasz; Joseph Kline; Stephen Knight; Delphine Le-Cunff; Scott List; Seong-Min Ma; Philippe Maillot; Jack Martinez; Niwa Masaaki; Yaw Obeng; George Orji; Brennan Peterson; Narenda Rana; David Seiler, Victor Vartanian; Andras Vladar; Yuichiro Yamazaki.

*Modeling and Simulation*—Jean-Charles Barbe, Augusto Benvenuti, Alex Burenkov, Mauro Ciappa, Wolfgang Demmerle, Andreas Erdmann, Wladek Grabinski, Tibor Grasser, Vincent Huard, Bert Huizing, Herve Jaouen, Andre Juge, An De Keersgieter, Gerhard Klimeck, Wilfried Lerch, Jürgen Lorenz, Wolfgang Molzer, Victor Moroz, Chandra Mouli, Jürgen Niess, Yon-Sup Pang, Hwasik Park, Paul Pfäffli, Peter Pichler, Yi-Ming Sheu, I.C. Yang

# **Table of Contents**

| Exect | utive                   | Summary                                                       | . 1 |

|-------|-------------------------|---------------------------------------------------------------|-----|

| 1.    | Intro                   | duction: The Ever Changing Environment                        | .2  |

| 2.    | Inter                   | net of Everything (IoE)                                       | .4  |

| 3.    | 2015                    | 5 ITRS 2.0 Edition and Moving Forward                         | . 5 |

| 4.    |                         | rall 2015 2.0 Process and Structure                           |     |

| .4.   | .1.                     | Background                                                    |     |

| .4.   | .2.                     | Roadmapping Process                                           |     |

| 5.    |                         | em Integration: ITRS 2.0 View of the new Ecosystem            |     |

| -     | .1.                     | Data Centers                                                  |     |

| -     | .2.                     | IoT and IoE                                                   |     |

|       | .3.                     | Mobility                                                      |     |

| .6.   | Hete                    | erogeneous Integration                                        |     |

| -     | . ı.<br>.2.             | 3D integration                                                |     |

| -     | .z.<br>.3.              | Wafer Level Packaging                                         |     |

| -     | .3.<br>.4.              | Difficult Challenges for SiP                                  |     |

| -     | . <del>.</del> .<br>.5. | Difficult Challenges for Heterogeneous Integration            |     |

|       | .6.                     | Heterogeneous Components                                      |     |

|       | .7.                     | Automobiles                                                   |     |

| .6    | .8.                     | Consumer Portable                                             |     |

| .6    | .9.                     | Consumer Wearable and Healthcare                              |     |

| .7.   | Con                     | nectivity                                                     | 26  |

| .7.   | .1.                     | RF & AMS Wireless                                             |     |

| .7.   | .2.                     | Photonic Transmitters                                         |     |

| .7.   | .3.                     | Fiber-optic communication                                     |     |

| .7.   | .4.                     | Local Area Networks                                           |     |

| .7.   | .5.                     | Long Distance Connectivity                                    |     |

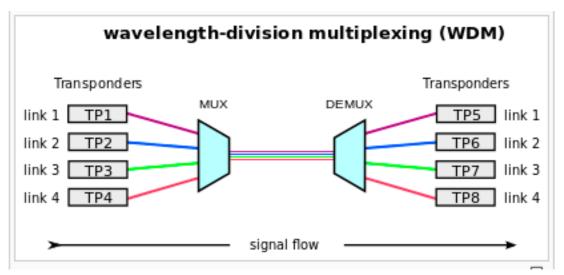

|       | .6.                     | Wavelength-Division Multiplexing (WDM)                        |     |

|       | .7.                     | Telecommunications (Long Range Communications)                |     |

| .8.   |                         | e Moore                                                       |     |

| -     | .1.                     | Overall Transistor Trends                                     |     |

|       | .2.                     | Memory Trends.                                                |     |

| .0    | .3.                     | 5                                                             | 33  |

| .9.   | Drivi                   | ing the IC industry to the limits of CMOS and Beyond          |     |

|       | .1.<br>.2.              | Future Memories                                               |     |

| -     | .2.<br>.3.              | Storage Class Memory Devices                                  |     |

|       | .0.<br>.4.              | Emerging Logic and Alternative Information Processing Devices |     |

|       | .5.                     | Devices for CMOS extension                                    |     |

|       | .6.                     | Beyond-CMOS devices                                           |     |

| 9     | .7.                     | Devices With Learning Capabilities                            |     |

| 9     | .8.                     | Emerging Computing Architectures                              |     |

| 9     | .9.                     | Logic Devices Benchmarking                                    |     |

| .10.  | Fa                      | actory Integration                                            | 47  |

| .1    | 0.1.                    | Factory Requirements                                          | 48  |

|       | 0.2.                    | Facilities Requirements                                       |     |

| .1    | 0.3.                    | Impact of Big Data of Factory Operations                      | 51  |

| .11.   | Challenges and Possible Solutions |  |

|--------|-----------------------------------|--|

|        | System Integration                |  |

|        | Heterogeneous Integration         |  |

| .11.3. | . Outside System Connectivity     |  |

| .11.4. | More Moore                        |  |

| .11.5. | Beyond CMOS                       |  |

|        | Factory Integration               |  |

# List of Figures

| Fig. 2.1 Internet Penetration                                                                                                                                                                          | 5    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 3.1 The Ideal MOS Transistor                                                                                                                                                                      | 6    |

| Fig. 3.2 The numbers of electrons on a floating gate will be reduced to 10 when design rules re the 10nm                                                                                               |      |

| Fig. 3.3 Toshiba's BiCS (Bit Cost Scalable)                                                                                                                                                            |      |

| Fig. 4.1 The New Ecosystem                                                                                                                                                                             | 8    |

| Fig. 4.2 The New Focus teams                                                                                                                                                                           | 8    |

| Fig. 4.3 Transition from ITWGs to FTs                                                                                                                                                                  | 9    |

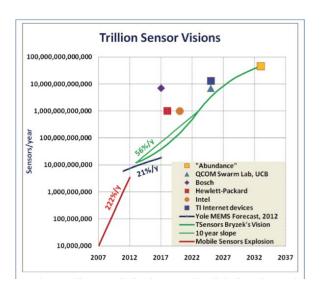

| Fig. 5.2 Sensors will populate the world of the IoE                                                                                                                                                    | . 14 |

| Fig. 5.3 The wireless world                                                                                                                                                                            | . 14 |

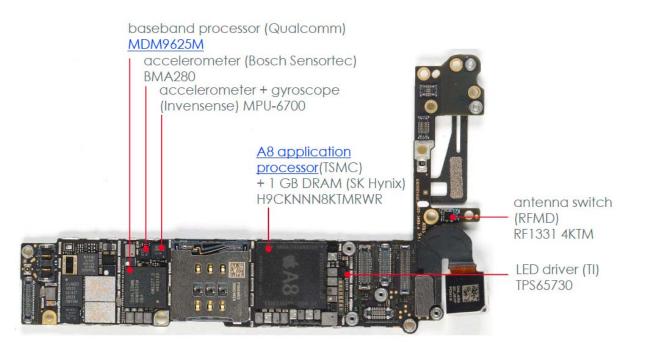

| Fig. 5.4 A8 key features and die layout                                                                                                                                                                | . 16 |

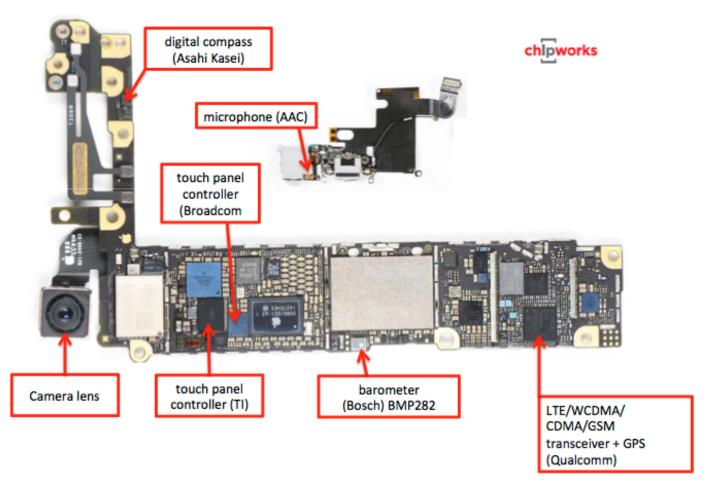

| Fig. 5.5 iPhone 6 Application Processor and phone layout                                                                                                                                               | . 16 |

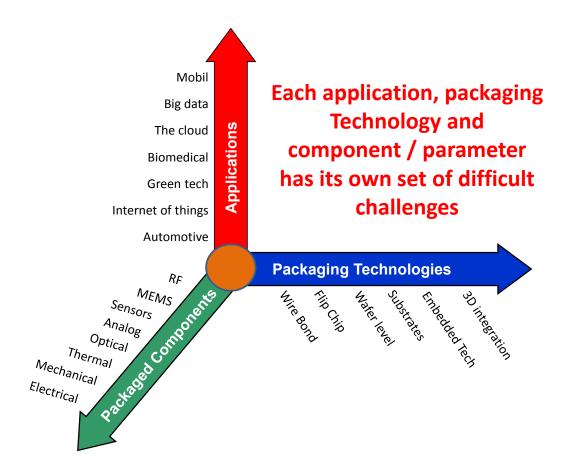

| Fig. 6.1 Elements incorporated into complex SiP packages through heterogeneous integration                                                                                                             | .17  |

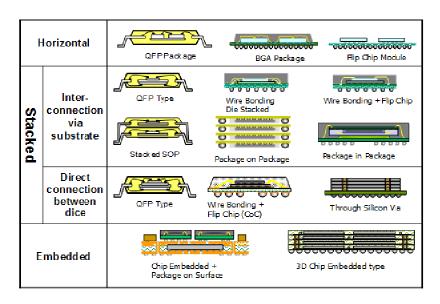

| Fig. 6.2 Categories of SiP                                                                                                                                                                             | . 18 |

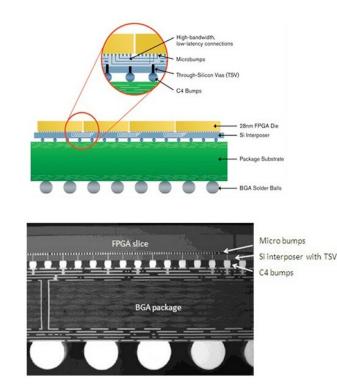

| Fig. 6.3 2.5D Interposer for Xilinx FPGA                                                                                                                                                               | . 19 |

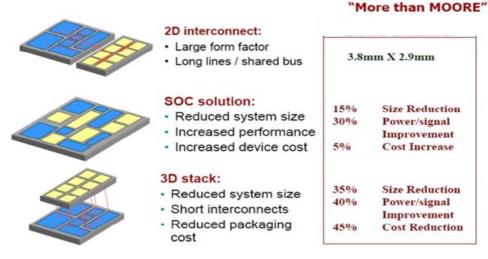

| Fig. 6.4 Driving Forces for 3D Integration                                                                                                                                                             | . 20 |

| Fig. 6.5 Examples of existing Wafer Level Packaging Types                                                                                                                                              | i    |

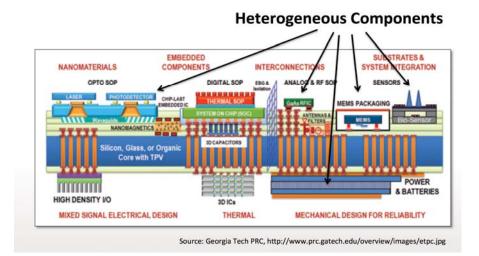

| Fig. 6.6 Illustration of Heterogeneous Components in a Heterogeneous System                                                                                                                            | . 23 |

| Fig. 6.7 Sensors bridge the world of Electronics with the world of humans                                                                                                                              | . 25 |

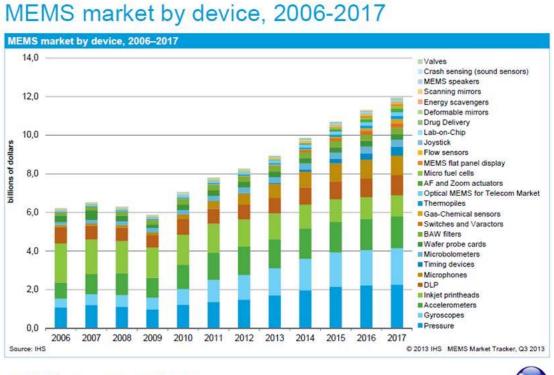

| Fig. 6.8 The multi-faceted market of MEMS                                                                                                                                                              | . 26 |

| Fig.7.1 WDM schematics                                                                                                                                                                                 | . 29 |

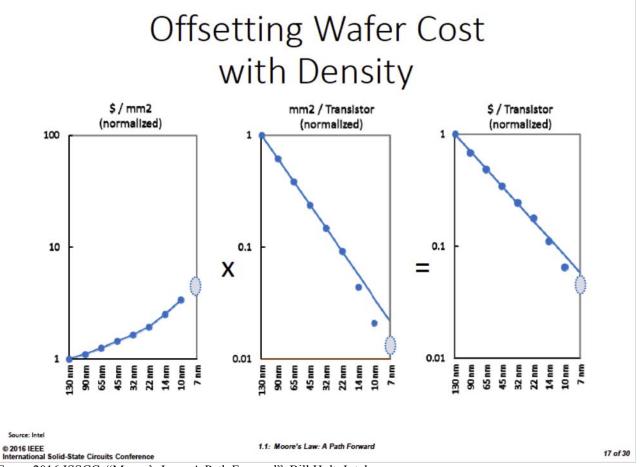

| Fig. 8.1 Increased transistor density enabled by FinFET                                                                                                                                                | . 35 |

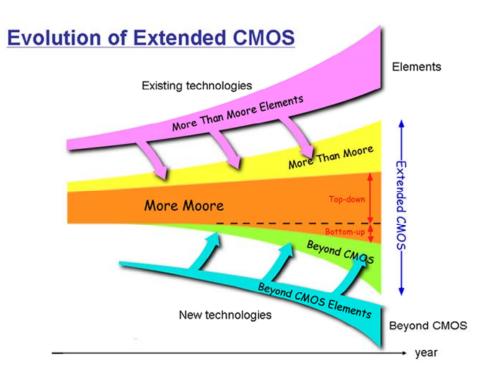

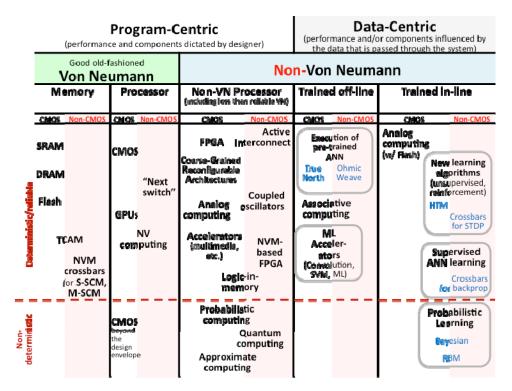

| Fig. 9.1 Relationships of More Moore, More-than-Moore, and Beyond CMOS devices (Courtes Japan ERD).                                                                                                    |      |

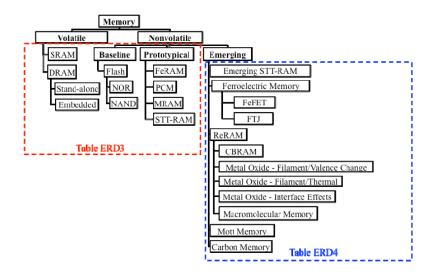

| Fig. 9.2 Taxonomy of emerging memory devices                                                                                                                                                           | . 41 |

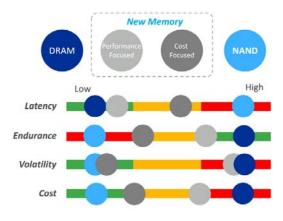

| Fig. 9.3 Comparison of performance of different memory technologies                                                                                                                                    |      |

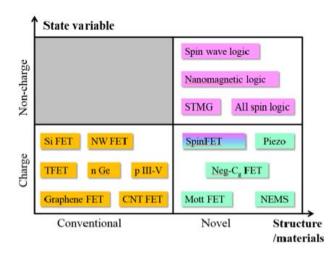

| Fig. 9.4 Taxonomy of options for emerging logic devices.                                                                                                                                               | . 43 |

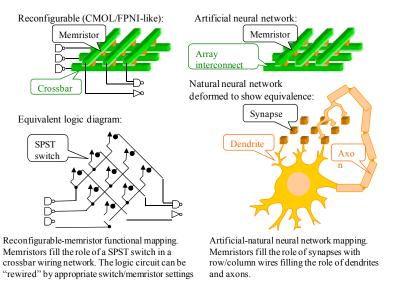

| Fig. 9.5 Two variants of learning devices for configuration                                                                                                                                            | . 45 |

| Fig. 9.6 Categories of computing architecture                                                                                                                                                          | . 46 |

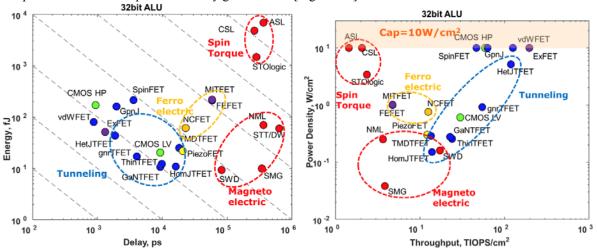

| Fig. 9.7 (a) Energy vs. delay plot of 32bit ALU built from benchmarked devices; (b) power vs. throughput of 32bit ALU built from these devices, reflecting power-constrained (< 10 W/cm <sup>2</sup> ) | 47   |

| Integration Integration                                                                                                                                                                                |      |

|                                                                                                                                                                                                        | 40   |

# List of Tables

| Table 1 Specification for SiP                                                                | 18  |

|----------------------------------------------------------------------------------------------|-----|

| Table 2 Examples of heterogeneous components with their key attributes for automotive, sma   | ırt |

| phone, wearable, and medical applications, exemplifying how their requirements may differ wi | th  |

| application                                                                                  | 24  |

# **EXECUTIVE SUMMARY**

For the past 50 years the Semiconductor Industry has marched at the pace of Moore's Law. Transistor scaling associated with doubling the number of transistors every two years has been and continues to be the unique feature of the semiconductor industry. As a consequence, as transistors became smaller they could also be switched from the off to the on state at faster rates while simultaneously became cheaper to manufacture. System integrators assembled new products utilizing the building block provided by the semiconductor industry but system integrators were barely able to complete assembling a new system when a yet new more powerful IC was becoming available. Any new technology generation enabled multiple new products with better performance than the previous ones. Integrated device manufacturers (IDM) were in full control of the pace at which the electronics industry was progressing by setting the marching pace at which the whole electronics industry ecosystem was moving forward. Therefore past editions of technology roadmaps concentrated on forecasting the rate of transistor scaling and how transistor density and performance affected the evolution of integrated circuits (IC).

In the past 15 years the advent of the Internet, the extensive deployment of Wi-Fi base stations, consumer acceptance of a broad variety of wireless mobile appliances plus the successful combination of fabless companies working in conjunction with foundries has completely changed the electronics industry. System integrators are nowadays able to conceive, design and realize any integrated circuit they wish without having to recur to integrate device manufacturers. System Integrators can nowadays integrate multiple functionalities in a single chip called System on Chip (SOC) or by means of integrating multiple dice in a single package called System in Package (SIP) as opposed to connecting multiple specialized ICs on a board. It is clear that these methods of integration are more efficient and less costly than acquiring several separate ICs (e.g., microprocessor, graphic processor, multiple memory types, usb etc.) and assembling them on a board. System integrators are by and large setting the pace of innovation for the electronics industry.

Each new technology generation produces faster transistors that can switch faster than those produced with the previous technology generation. In the past this electrical feature of transistors enabled microprocessors to operate at higher frequencies and therefore computer performance as measured by industry benchmarks, like measured by million of instruction executed per second (MIPS), continued to improve at very fast rates. Computer architecture has not changed since Von Neumann introduced its concept on how to perform computing in 1945. Through the years nobody paid too much attention to the fact that power consumption of integrated circuits kept on increasing with any new technology generation since the industry motto was: "*performance at any cost!*" This approach came to an end at the beginning of the past decade when fundamental thermal limits were reached by some ICs. Even though the transistor count has kept on increasing now and then at Moore's Law pace and transistors are able to operate with each new technology generation at higher frequency then before it has become practically impossible to keep on conjunctly increasing both of these factors due to physical limitations on power dissipation; one of the two feature (i.e., either number of transistor or frequency) had to level off in order to make the ICs capable to operate under practical thermal conditions. Frequency was selected as the sacrificial victim and it has stalled in the few GHz since the middle of the previous decade.

These limitations on maximum useable frequency have impacted the rate of progress of the computer industry that has been compelled to develop such methods as complex software algorithms and clever instruction management to improve performance to partially compensate for the aforementioned conditions. The architecture of the microprocessors has changed from single core to multi-core. In this arrangement the processor can run in the few GHz range while the output rate is increased multifold by combining the output of multiple cores to produce the output signal. Unfortunately this parallel type of solution cannot be used in all cases since some problems can only be solved in a serial way. However, these performance limitations did not impact the development and expansion of the mobile Internet society. Consumers began accessing the Internet via desktop appliances and then progressively got used to access it via mobile multipurpose appliances. Reaching any source of information via the Internet takes tens of milliseconds due to the speed at which signals can travel on any interconnect lines so microprocessors operating in the few GHz frequency range are more than adequate to handle the communication traffic. Cell phones began operation in the 90s using frequencies in the 800-900MHz ranges in accordance with specifications of the Global System for Mobile Communications (GSM). These operational frequencies evolved with the use of 4G and LTE to the 2,500-2,700MHz ranges. Operation in these frequency ranges is still well within the capabilities of ICs. In the past 10 years, cell phones and mobile appliances in general have become a viable means of accessing the Internet. Cell phone power consumption is typically below 5 watts so this value is well within the thermal limits of ICs operation. Most recently, access to the Internet via Wi-Fi has been continuously increasing since the areas of coverage are continuously extending; mobile appliances have become the most convenient means of communication and access to any source of information anywhere at any time.

The IC industry has also contributed to provide valuable technology building blocks to other industries and by so doing enabling new devices like micro-mechanical systems (MEMS), flat panel displays, multiple sensors and so on. All of these somewhat dissimilar technologies have been readily included into mobile appliances by means of heterogeneous integration.

The insatiable demand for information has led to the creation of gigantic clusters of servers and memory banks named Data Centers. In this environment performance is still the name of the game and using complex cooling systems can mitigate power issues. Power consumption of Data Centers is rapidly escalating into the hundreds of Megawatts range. Communications within the Data Centers and for long distances is handled via fiber optics because of their stellar low rate of attenuation.

All of the above systems specifications dictate the requirements for the semiconductor industry.

Minimal power consumption of transistor operation has become the main requirement for the semiconductor industry dictated by the new ecosystem of the electronics industry. On the other hand, the requirement for a continuously increasing number of transistors according to Moore's Law continues unabated. As an example this can be demonstrated by observing that the number of transistors in the latest cell phone Application Processors has kept on increased from the 1Billion transistors of the A5 to 2Billions for A6 to 3Billion for A6X. It is projected that the upcoming A9 will range from 2.7 to 4.5 Billions depending upon the application.

To satisfy the product demand for higher transistor counts the semiconductor industry is approaching a new era of scaling.

Geometrical scaling characterized the 70s, 80s and 90s. This was the first generation of transistor scaling. Major material and structural limitations were identified in the mid-90s and the research community initiated the foundation of a new scaling approach that was heralded by the ITRS in 1998. This was named Equivalent Scaling. Strained silicon, high-k/metal gate, FinFET and use of other semiconductor material (e.g., Germanium) represent the main features of this scaling approach.

As features approach the 10nm range and below it becomes clear that the semiconductor industry is running out of horizontal space.

Memory products have always been the leaders in transistor density and so it is not surprising that the solution to this problem is coming from Flash memories. Multiple companies have announced that future products will fully utilize the vertical dimension. This is not too dissimilar from the approach taken in Manhattan, Tokyo, Hong Kong or similarly highly crowded places to deal with space limitations: skyscraper have become the standard approach to maximize "packing density".

For the reasons exposed above the new scaling method is called "3D Power Scaling".

In the Beyond CMOS section the reader will find multiple new and exciting devices that after 10 years of research are demonstrating the possibility of becoming key players in the next decade.

Finally, all these exciting technologies need to be realized in a High Volume Manufacturing (HVM) Factory. Controlling nanometer features across 300mm wafers remain an amazing challenge that the industry is managing across the globe but will this be possible on 450mm wafers? Real time data collection, analysis and consequent disposition of wafers via a fully automated material handing system will remain the goals of the HVM Factory in the next decade until "full light out" operation is reached.

# **1. INTRODUCTION: THE EVER CHANGING ENVIRONMENT**

The Semiconductor Industry was born in the 70s as an electronics component industry with three main business drivers. The first driver consisted in providing cost effective memory devices to the computer industry. Memories soon became the undisputed volume leaders.

The second driver consisted in production of application specific integrated circuits (ASIC). Any company that required new and unique functionalities to realize novel products developed a set of functional and electrical targets that were communicated to one or more semiconductor manufacturers. The latters turned these targets into specifications for one or more Integrated Circuits (IC) but all the Intellectual Properties (IP) belonged to the companies that commercialized the final produces and not to the IC manufactures.

Thirdly, ICs allowed cost effective integration of simple building blocks used in the design of many systems. These ICs typically consisted in small logic gates (RTL, DTL, TTL, NAND, J-K Flip-Flop etc.) and operational amplifiers ( $\mu$ A 709,  $\mu$ A 741 etc.) just to mention a few. Customers demanded pin-out and functionality standardization for memory devices while ASIC products were customer specific. Logic devices reprogrammable by software (e.g., microprocessors) were developed to minimize design cycle time and to pave the way for subsequent high volume ASIC devices once the product functionality was demonstrated.

#### Phase 1

In the 70s and 80s *system specifications were solidly in the hands of system integrators*. New DRAM memory technologies were introduced every three years to keep up with the introduction of new computer systems. Typically a new generation of computers required a four-fold increase in memory and that it is why the famous "4X/3Years" memory density and pace for introduction of new memory technologies was established. This 4x increase in memory size was realized by means of decreasing transistor features but also by substantially increasing the die size and this had a very negative impact on product cost as fewer dice were made available by this approach on each wafer. In the long rum the latter resulted in a limiting factor for DRAM memory technologies generated requirements for development of new building blocks for the manufacturing process that required better equipment; makers of logic devices were operating on a 4 year cycle trailing behind memory manufactures and therefore adopted a subset of similar process blocks and most of the same equipment developed for memory technologies.

#### Phase 2

In the early 90s the very profitable Personal Computer market required more complex and faster microprocessors. To feed the growth of this market the makers of logic ICs were compelled to accelerate the introduction of new technologies from 4-years cycle to a more aggressive 2-year cycle to support faster introduction of new products. In the late 90s memory makers were compelled to follow the 2x/2-year introduction cycle when eventually the die size of new memory products became too large to be economic. The strong correlation between technology scaling and electrical performance of most ICs, as for instance higher operational frequency, made the introduction of new higher performance products, and PC in particular, completely subordinate to enhanced performance of microprocessors. This strong scaling-product correlation made those IC makers that controlled the introduction of leading technologies the real controllers of the whole electronics industry. As a direct result of this trend, a *substantial part of system specifications, performance and profits shifted in the hands of IC manufacturers*. After all this ecosystem was beneficial to everybody in the electronics industry and as long as performance of microprocessors and computers built accordingly to Von Neumann architecture was benefitting form higher operational frequency, the entire semiconductor industry revenue continued to grew. The IC industry grew at an average pace of 17%/year during this period. IDM manufacturers of logic devices were able to capitalize the most from this new shift in the balance of power.

Like it happens very often, the IC industry believed in the 90s that this market model (i.e., faster processors supporting larger amounts of memory supporting continuous growth for the semiconductor and electronics industries) was going to last forever but things were going to change in a very dramatic way with the advent of the new century.

#### Phase 3

#### A completely new ecosystem emerged during the past decade:

- First of all, the relatively moderate incremental cost of technology development from one generation to the next (10% or below) fueled the aggressive bi-annual introduction of new semiconductor technologies that allowed ICs, consisting of hundreds of million of transistors, to be produced in a very cost effective manner. This made it possible to integrate extremely complex systems constituted of logic, memory, graphics and other functionalities on a single die at a very attractive cost. Furthermore, progress in packaging technology enabled the placement of multiple dice within a single package. These categories of devices were defined as system on chip (SOC) and system in package (SIP), respectively.

- Second, manufacturers of integrated circuits offering foundry services were able to provide the capability of realizing complex systems either on a single die or in a single package (the "New ASICs") at very attractive costs. This led to the emergence of a very profitable business model whereby fabless companies could generate IC designs, while actual wafer production was done elsewhere by a foundry company.

- Third, sophisticated process equipment, developed for the production of advanced integrated logic and memory circuits, proliferated to adjacent technology fields making the realization of flat panel displays (FPD), MEMS

#### **4 Executive Summary**

sensors, radio components and passives, etc., possible at very reasonable costs. All these different technologies were then integrated in a single revolutionary system. This new way of making products by integrating multiple heterogeneous technologies successfully emerged around the middle of the previous decade and was named "More than Moore" (MtM).

Under these conditions system integrators were once again in the position to fully control system design and product integration.

In the same timeframe, the successful adoption of the Internet and the rapid rise of world-wide adoption of mobile phones promoted the extensive deployment of fiber optic cables and the proliferation of multiple wireless technologies ranging from communication satellites to tens of thousands of "base stations" which enabled an unprecedented level of global and mobile connectivity.

This ecosystem facilitated also the creation of completely new and unexpected markets of which the many "Social Networks" represents one of the latest examples.

Intense research on how to enhance the functionality of mobile devices continues to bear fruits and has made them the ultimate instrument that allows customers to enjoy ubiquitous access to any type of communication and information material. Furthermore, new additional capabilities enabled by the integration of computer and communication technologies are fueling research on yet broader markets. Substantial in road is being made in making available to customers multiple sensorial inputs that are remotely generated. Among other things this technology is opening the way to enabling remote medical interaction between doctors and patience. Multiple companies also herald the arrival in the next few years of self-driving automobiles as another example of the integration of powerful on-board computers connected via Wi-Fi to navigation information and capable of simultaneously collecting information from multiple sensors operating from optical to RADAR frequencies.

All of the above elements have been referred to as the "Internet of Things" (IoT) or recently even more generally as the "Internet of Everything" (IoE) since any aspect of society ranging from human to objects to everything you can think of is becoming an "element" connected to and by the Internet. Innovative products introduced by telecommunication companies, by companies operating data centers and by content providers are battling for dominant positions in this newly created market. It is clear that all of these innovations could not have occurred without the support of the semiconductor industry that has provided the building blocks for all the above applications.

It was simple to understand the role of ICs in the product chain up to the 90s but with this completely different ecosystem we must ask ourselves an important and fundamental question:

"What is the role of the semiconductor industry in this new ecosystem?"

# 2. INTERNET OF EVERYTHING (IOE)

The ITRS already emphasized the importance of the Internet in previous reports but in the past 5 years IoT has evolved into IoE and it is important to dedicate a paragraph to this subject since the IoE is shaping the whole society and creating multiple industries.

The US Department of Defense awarded contracts as early as the 1960s for packet network systems, including the development of the ARPANET (which would become the first network to use the Internet Protocol.)

Access to the ARPANET was expanded in 1981 when the National Science Foundation (NSF) funded the Computer Science Network (CSNET). Since the mid-1990s, the Internet has had a revolutionary impact on culture and commerce, including the rise of near-instant communication by electronic mail, instant messaging, voice over Internet Protocol (VoIP) telephone calls, two-way interactive video calls, and the World Wide Web. This worldwide connectivity has created new phenomena like social networking and online shopping. Increasing amounts of data are transmitted at higher and higher speeds over fiber optic networks operating at 1-Gbit/s, 10-Gbit/s, soon 40-Gbit/s and more. The Internet's takeover of the global communication landscape was almost instant in historical terms: it only communicated 1% of the information flowing through two-way telecommunications networks in the year 1993, already 51% by 2000, and more than 97% of the telecommunicated information by 2007. Today the Internet continues to grow, driven by evergreater amounts of online information, commerce, entertainment, and social networking. Access to the Internet was

THE INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS 2.0: 2015 LINK TO ITRS 2.0, 2015 FULL EDITION DETAILS originally done via desktop computers but the introduction of smart phones in 2007 and tablets in 2010 has revolutionized the way people interact via the Internet. The world of communications has truly become a wireless, ubiquitous and continuously interconnected world.

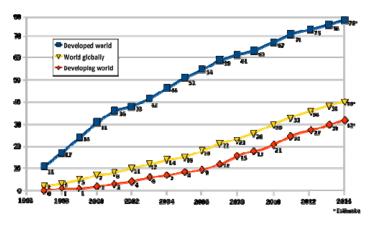

#### Fig. 2.1 Internet Penetration

Until 10 years ago the Internet was mostly used as a means of collecting information and communications but progressively it evolved into a commercial instrument through which people could book services, acquire goods, pay bills and so on. This however was just the beginning since different types of cameras and sensors began to be connected to the Internet and by so doing opening new exciting uses and applications. At present the Internet of Things allows objects to be sensed and controlled remotely across existing network infrastructure, creating opportunities for more direct integration between the physical world and computer-based systems, and resulting in improved efficiency, accuracy and economic benefit

As the list of elements that can be connected to the Internet keeps on increasing a new term has been coined out: The Internet of Everything (IoE). The term IoE expands on the concept of the "Internet of Things" in that it connects not just physical devices but quite literally *everything* by getting them all on the network. IoE works to connect more devices onto the network, stretching out the edges of the network and expanding the roster of what can be connected. IoE has a major play in all industries, from retail to telecommunications to banking and financial services. It also opens the door to remote medicine in which a doctor can analyze results of tests remotely taken by patients and evaluates them. Of course placing all this personal information on the web or accessible via the web poses a severe challenge for security. Almost everyday we can hear news of hackers stealing valuable information and it is imperative that appropriate measures are taken to prevent these problems but despite this more and more people are willing to "venture" in the IoE since the benefits offered by the many capabilities offered by the IoE are overwhelming.

With this all said and done it is important to remember that the IoE could not happen if semiconductors did not power communication devices, data centers, routers and sensors. The advent of Foundries and Fabless companies enabled the customization of semiconductor products that now cover all the aspect of IoE and it would be a mistake to assume that the semiconductor industry is by now a mature industry and it has not much more to offer. The advent of third phase of device integration (i.e., 3D Power Scaling) plus the many new capabilities associated with the introduction of revolutionary materials in the semiconductor industry will revolutionize how computers are built. New Computers built with revolutionary Architectures enabled by New Devices will be surrounded from top to bottom with a variety of new sensorial capabilities that will offer new and exciting options to system designers (see Rebooting Computing section for more details).

But we should not be overwhelmed by the endless applications that we can dream of since in the end, from a system point of view, the IoE is nothing more than a distributed computer capable of accessing via the Internet (Routers and base stations) remote memories (Data Centers), connected to a variety of sensors and actuators. Software and protocols then tie it all together.

In the near future the IoE will allow customers to retrieve, analyze, assemble, summarize information and provide also actionable recommendations. Be careful, the IoT will soon think for you!

# 3. 2015 ITRS 2.0 EDITION AND MOVING FORWARD...

#### "Nothing is New, but never is the same"

The foundations of IC industry were laid out with the invention of the self-aligned silicon gate planar process in the late 1960s. Moore's predictions of the doubling of transistor generated on an annual and then bi-annual pace formulated in 1965 and in 1975 in conjunction with Dennard's scaling guidelines led to the growth of the semiconductor industry until the beginning of the last decade.

#### 6 Executive Summary

This was the (First) Era of Geometrical (classical) Scaling. This type of scaling was the foundation of the National Technology Roadmap for Semiconductors (NTRS) initiated in 1991.

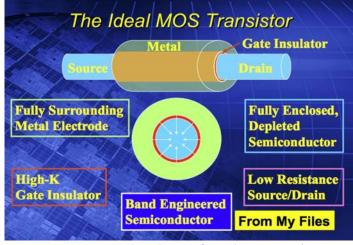

The ITRS laid out the foundations of the (Second) Era: Equivalent Scaling (e.g., strained silicon, high-K/metal gate, Multigate transistors and use of non-silicon semiconductors in general) between 1998 and 2000.

1998 ITRS: Equivalent Scaling vision of required transistor innovation Fig. 1

#### Fig. 3.1 The Ideal MOS Transistor

The implementation of these technologies successfully supported the growth of the semiconductor industry in the past decade and it will continue to do so until the end of the present decade and beyond.

In the next decade ITRS 2.0 predicts that the advent of the third phase of scaling "*3D Power Scaling*" will become the driver of the rejuvenated semiconductor industry and this *answers the question* posed before about the future of the semiconductor industry: "*Yes the semiconductor industry will continue to be a key enabler of the IoE*"

Moore's Law is now entering into a third phase characterized by vertical integration and performance specifications driven towards reduction of power in either the active or the stand-by modes.

It is important to realize that despite the many announcements of the end of Moore's Law it is expected that the transistor density of future IC will continue to increase in the foreseeable future at historical rates.

# Even though producers of logic integrated circuits have been the most prominent champions of Moore's Law it is also true that *producers of memory devices have been the leaders in production of Integrated Circuits with the tightest tolerances and the smallest dimensions. In few words, they have been the real drivers of Moore 'Law and will continue to do so in the future.*

DRAM producers already dealt with space problems as far back as the "Megabit" memory generation. In order to build capacitors back then with enough storage capacity it would have required more silicon area than the area needed to build the transistors and therefore DRAM producers adopted stack capacitor or trench capacitor solutions to take advantage of the vertical dimension either above or below the surface of the silicon.

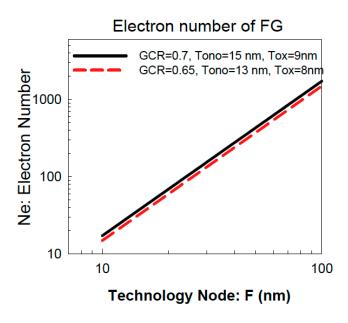

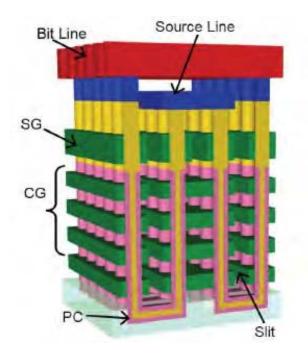

Nowadays, Flash memory producers are facing a similar problem since they are running out of horizontal space, cost of producing integrated memory circuits of small dimensions keeps on rising while the number of stored electrons in the floating gate keeps on decreasing [Fig.3.2]. To eliminate these problems Flash memory producers have already demonstrated and announced several new products that stack multiple layers of memory on top of each other in a single integrated circuit [Fig. 3.3]. As many as 32 and 48 layers of Flash memory have been reported. Flash memory devices constituted by more than 100 layers have been predicted. Flash memory producers promise a transistor density acceleration of memory ICs realized with 3D technology *far exceeding the historical 2x/2year rate*. Moore's Law is once again on the verge of a substantial acceleration.

*Fig. 3.2 The numbers of electrons on a floating gate will be reduced to 10 when design rules reach the 10nm*

Fig. 3.3 Toshiba's BiCS (Bit Cost Scalable)

Once again it is relevant to notice that, as a method of manufacturing the densest IC reaches physical limits a new, more powerful one, takes over the role of carrying the industry forward for at least one or two decades. Despite this recurrent "demise and resurgent" sequence of events many prophesies about the end of Moore's Law have been published every 10 years or so. May be the best way to eliminate these recurrent misunderstandings consists in capturing in a single phrase

the essence of these repeating events. This goal could be accomplished by using a well-known and familiar saying and morphing it to epitomize the most relevant historical trend of the semiconductor industry as follow:

# "Moore's Law is dead, long live Moore's Law!"

# 4. OVERALL 2015 2.0 PROCESS AND STRUCTURE

## 4.1. BACKGROUND

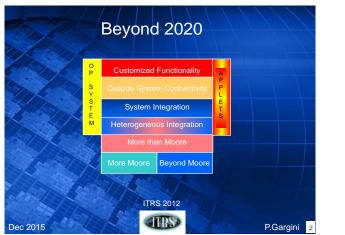

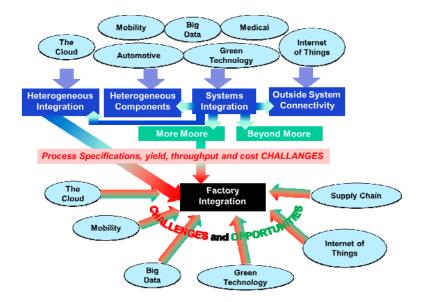

As outlined before the advent of Fabless Design Houses and Foundries has revolutionized the way in which business is done in the new semiconductor industry, System Integrators have regained full control of the business model. This implies that system requirements are set at the beginning of any new product design cycle and step by step related requirements percolate down through the manufacturing production chain to the semiconductor manufactures. No longer a faster microprocessor triggers the design of a new PC but on the contrary the design of a new smart phone generates the requirements for new ICs and other related components. Under these conditions it became clear in 2012 that the ITRS needed to adapt and morph to the new ecosystem [Fig 4.1]. It was anticipated that this transformation process would take sometime and it was decided that the 2013 ITRS was going to be the last of its kind. Next, 2014 and 2015 were going to be dedicated to the construction of a new roadmap that was named ITRS 2.0.

The new ecosystem needed to be viewed though a top-down viewer and for this purpose the elements outlined in Fig. 4 led to the formation of seven Focus Teams [Fig.4.2]

Fig. 4.1 The New Ecosystem

Fig. 4.2 The New Focus teams

# 4.2. ROADMAPPING PROCESS

The ITRS process and content has kept on evolving to match the needs of the semiconductor industry. Collaboration of industry and research continues to be essential to understand the technical challenges and future needs in the various spectra of micro- and Nano-electronics. Over the past few years, the ITRS teams have worked closely to assess emerging technologies. They have been preparing to support the technical needs of both the new world of interconnectedness between humans and hardware (IoE) as well as how to handle the complex world of information processing known as Big Data. These examples are only part of the new frontiers of inventions and discoveries. As these new focus topics continue to emerge, the ITRS teams will continue to determine what this means for the global electronics industry. The industry must define the new drivers to help it stay on a path of productivity and profitability, while promoting environmental health and encouraging areas of innovation for new scientists and technologists

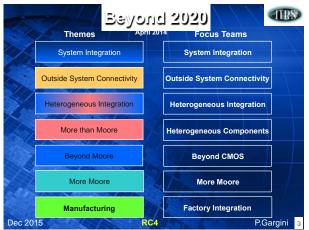

The most relevant subjects of the ITRS were originally divided among eleven International Technology Working Groups (ITWGs). As time went by the industry became more complex and the number of ITWGs increased to 17 in 2013. During the 2014-15 timeframe ITRS 2.0 was reorganized into 7 Focus Teams.

For the 2015 ITRS 2.0 the Focus Teams are the following:

- System Drivers

- Heterogeneous Integration

- Heterogeneous Components

- Process Integration, Devices, and Structures

- Outside System Connectivity

- More Moore Beyond CMOS

- Factory Integration

The existing 17 ITWGs were redistributed according to this new organization [Fig 4.3]. All the ITWGs are still operational but most of their output is channeled into the Focus team. An additional section "For Expert Only" includes additional detailed information provided by the ITWGs that was not completely included into the Focus Teams. The Focus Teams and the ITWGs are composed of experts from industry (chip-makers as well as their equipment and materials suppliers), government research organizations, and universities.

|                                                     | ITRS 2.0 |     |    |    |    |    |    |

|-----------------------------------------------------|----------|-----|----|----|----|----|----|

|                                                     | 1        | 2   | 3  | 4  | 5  | 6  | 7  |

| 2013 ITRS ITWGs                                     | SI       | OSC | HI | нс | MM | BC | FI |

| 1System Drivers                                     | X        |     |    |    |    |    |    |

| 2 Design                                            | X        |     |    |    |    |    |    |

| 3Test and Test Equipment                            |          |     | x  |    |    |    |    |

| 4Process Integration, Devices and Structures (PIDS) |          |     |    |    | X  |    |    |

| 5Emerging Research Devices (ERD)                    |          |     |    |    |    | x  |    |

| 6Emerging Research Materials (ERM)                  |          |     |    |    |    | x  |    |

| 7Front End Process                                  |          |     |    |    | X  |    |    |

| 8Lithography                                        |          |     |    |    | X  |    |    |

| 9Interconnect                                       |          |     |    |    | X  |    |    |

| ORF and A/MS Techonologies                          |          | X   |    |    |    |    |    |

| 1Yield Enhancement                                  |          |     |    |    |    |    | X  |

| 2Factory Integration                                |          |     |    |    |    |    | X  |

| 3Assembly and Packaging                             |          |     | x  |    |    |    |    |

| 4Enviroment, Safety and Health                      |          |     |    |    |    |    | x  |

| 5Metrology                                          |          |     |    |    | x  |    |    |

| 6 Modeling and Simulation                           |          |     |    |    | x  |    |    |

| 7MEMs                                               |          |     |    | x  |    |    |    |

## 4.3. 2015 ITRS 2.0 FOCUS TEAMS

#### System Integration (SI)

The mission of the System Integration (SI) chapter in ITRS2.0 is to establish a top-down, system-driven roadmapping framework for key market drivers of the semiconductor industry drivers in the 2015-2030 period. The SI chapter is currently developing and constructing roadmaps of relevant system metrics for mobile, datacenter and Internet of Things (IoT) drivers.

#### **Heterogeneous Integration (HI)**

Heterogeneous Integration refers to the integration of separately manufactured components into a higher-level assembly that in the aggregate provides enhanced functionality and improved operating characteristics. In this definition components should be taken to mean any unit whether individual die, MEMS device, passive component and assembled

package or sub-system that are integrated into a single package. The operating characteristics should also be taken in

its broadest meaning including characteristics such as system level cost-of-ownership.

The mission of Heterogeneous Integration Focus Team is to provide guidance to industry, academia and government to identify key technical challenges with sufficient lead-time that they do not become roadblocks preventing the continued progress in electronics that is essential to the future growth of the industry and the realization of the promise of continued positive impact on mankind. The approach is to identify the requirements for heterogeneous integration in the electronics industry through 2030, determine the difficult challenges that must be overcome to meet these requirements and, where possible, identify potential solutions.

#### Heterogeneous Components (HC)

Heterogeneous Components are electronic devices that are manufactured using micro and Nano fabrication technologies and assembled together into the heterogeneous systems. The Heterogeneous Components Chapter identifies trends in high-market-growth-potential applications, determines the device performance requirements that are needed to enable those applications, and uses this information to discover technology gaps that must be solved in order to produce the future products that are envisioned by the roadmap.

The Mission of Heterogeneous Components Focus Team is to provide industry, academia and government to identify key technical challenges related to new heterogeneous components needed by the IoE ecosystem.

#### **Outside System Connectivity (OSC)**

The mission of OSC consist in identify and assess capabilities needed to connect most elements of the Internet of Everything (IoE) and highlight technology needs and gaps. This includes supporting connection of a broad range of sensors, devices, and products and to support information communication, processing and analysis for many applications (i.e. mobility, energy, health, and others) with wire line, wireless and optical interconnect technologies.

#### More Moore (MM)

MM Focus Team in ITRS provides physical, electrical and reliability requirements for logic and memory technologies to sustain More Moore (PPAC: power, performance, area, cost) scaling for big data, mobility, and cloud (IoT and server) applications and forecast logic and memory technologies (15 years) in main-stream/high-volume manufacturing (HVM)

#### Beyond CMOS (BC)

The goal of this Focus Team is to survey, assess and catalog viable new information processing devices and system architectures due to their relevance on technological choices. It is also important to identify the scientific/technological challenges gating their acceptance by the semiconductor industry as having acceptable risk for further development. Another goal is to pursue long-term alternative solutions to technologies addressed in More-than-Moore (MtM) ITRS entries.

This is accomplished by addressing two technology-defining domains: 1) extending the functionality of the CMOS platform via heterogeneous integration of new technologies, and 2) stimulating invention of new information processing paradigms.

#### Factory Integration (FI)

The Factory Integration (FI) focus area of ITRS 2.0 is dedicated to ensuring that the semiconductor-manufacturing infrastructure contains the necessary components to produce items at affordable cost and high volume. Realizing the potential of Moore's Law requires taking full advantage of device feature size reductions, new materials, yield improvement to near 100%, wafer size increases, and other manufacturing productivity improvements. This in turn requires a factory system that can fully integrate additional factory components and utilize these components collectively to deliver items that meet specifications determined by other ITRS 2.0 focus areas as well as cost, volume and yield targets.

# 5. SYSTEM INTEGRATION: ITRS 2.0 VIEW OF THE NEW ECOSYSTEM

In providing a top-down view of the new ecosystem it is necessary to have some simple depiction of what is under study including some basic definitions

ITRS 2.0 has developed also several tables to capture all of these elements and the reader will be able to find detailed information in the chapters addressing these subjects.

The executive summary presents a succinct overview of the above elements progressing from system requirement all the way to device specifications.

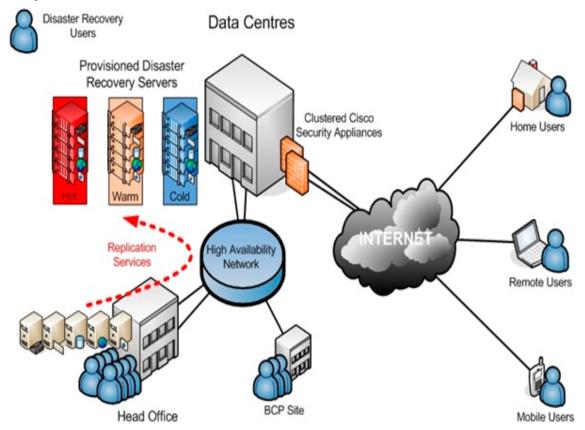

Fig.5.1 Internet: Example of Data Centers and Connectivity

## **5.1. DATA CENTERS**

Data centers are physical or virtual infrastructure [Fig. 5.1] used by enterprises to house computer, server and networking systems and components for the company's information technology (IT) needs, which typically involve storing, processing and serving large amounts of mission-critical data to clients in a client/server architecture.

In order to improve processing performance the IC industry has adopted a multi-core architecture for any type of Processors. This technical approach derives from the power limitations imposed by operating with a single core. Multiple cores, however operating at a lower frequency than a single core can provide enhanced output by processing information in a parallel way.

The increased demand for information processing in a data center will drive a 30-fold increase in the number of cores.

#### **Data Centers**

| Contraction    |                                        |        |       |          |        |        |        |        |         |

|----------------|----------------------------------------|--------|-------|----------|--------|--------|--------|--------|---------|

| Categories     | Year                                   | 2015   | 2017  | 2019     | 2021   | 2023   | 2025   | 2027   | 2029    |

|                | Number of Cores (K)                    | 360    | 1044  | 3008     | 4935   | 5825   | 7578   | 8967   | 10602   |

|                |                                        |        |       |          |        |        | 12626  | 37879  |         |

|                | Total Memory Storage (PB)              | 300    | 1559  | 4676     | 14029  | 42088  | 4      | 2      | 1136377 |

| Data<br>Center | Area of One Server Building (MSF)      | 0.5    | 0.9   | 1.6      | 2.2    | 2.2    | 2.42   | 2.42   | 2.42    |

| center         | Total Power Consumed by                | 0.5    | 0.5   | 1.0      |        |        | 2.72   | 2.72   | 2.72    |

| Global         | Datacenter (MkWh)                      | 779.8  | 839   | 1004.7   | 1137.2 | 1226.1 | 1380.7 | 1635.6 | 2044.3  |

|                | Total Switching Capability of          |        |       |          |        |        |        |        |         |

| Indicators     | Datacenter BW (Tb/s)                   | 1000   | 2512  | 6309     | 10000  | 15849  | 25119  | 39811  | 63096   |

|                | Data Center Efficiency (GFLOPS/W)      | 2.4    | 4.9   | 10       | 17     | 24     | 33.9   | 47.9   | 67.8    |

|                | Server Units/Rack                      | 40     | 40    | 40       | 40     | 40     | 40     | 40     | 40      |

|                | Number of Cores/socket                 | 18     | 29    | 47       | 59     | 74     | 93     | 117    | 147     |

| Servers        | Power /Single Server Unit (W)          | 700    | 700   | 700      | 700    | 700    | 700    | 700    | 700     |

|                | Main Memory / Single Server Unit       | 22     | 45    | <u> </u> | 76     | 04     | 400    | 420    | 454     |

|                | (GB)<br>Power Consumed by Cores/single | 32     | 45    | 64       | 76     | 91     | 108    | 129    | 154     |

|                | socket (W)                             | 165    | 159   | 153      | 149    | 145    | 141    | 137    | 133     |

|                | Network Bandwidth/Unit (Gb/s)          | 40     | 40    | 100      | 100    | 100    | 400    | 400    | 400     |

| Switching      | Network Bandwidth/Rack (Gb/s)          | 1600   | 1600  | 4000     | 4000   | 4000   | 16000  | 16000  | 16000   |

|                | Rack Switch Capacity BW (Gb/s)         | 1200   | 1200  | 3000     | 3000   | 3000   | 12000  | 12000  | 12000   |

|                | Power efficiency (Grid                 |        |       |          |        |        |        |        |         |

|                | delivery/Data Center Use)              | 0.55   | 0.57  | 0.59     | 0.61   | 0.63   | 0.65   | 0.67   | 0.69    |

|                | Power Consumed by Networking           |        |       |          |        |        |        |        |         |

| Power          | and Switching (MkWh)                   | 21.91  | 55.05 | 138.26   | 87.66  | 138.93 | 220.19 | 348.97 | 553.08  |

|                | Power Consumed by Storage              | 0.0657 | 0.259 | 0.449    | 0.778  | 1.347  | 2.334  | 4.043  | 7.004   |

|                | Power Consumed for facility            |        |       |          |        |        |        |        |         |

|                | cooling (MkWh)                         | 38.99  | 55.02 | 86.13    | 237.31 | 264.26 | 307.03 | 374.89 | 482.56  |

Data Centers operate as repository of data and given the insatiable need expressed by the user for more and more data it is expected that the requirement for memory storage will be the fastest growing item in the ITRS 2.0 Horizons an almost a 4000-fold increase in memory is forecast.

Under these conditions the area of the building will keep on increasing by 5x. These requirements will more than double the power requirements as measured in GWh (or MKWh). In order to control the rate of increase in power it is mandatory that the power of each server and the number of servers/rack be kept constant across the next 15 years.

Moving information within the Data Center and moving data to the network and receiving data from the network is of fundamental importance for the efficient operation of the Data Center and its connection to the Internet as an efficient means of communication to the users. Switching bandwidth per unit is presently operating at 40Gb/sec but it will need to reach the 400 Gbit/sec by 2025. This will require that the Network Bandwidth /rack will need to reach the 16,000 Gb/sec range to feed the insatiable need for data requested by the network.

A severe concern is constituted by the amount of energy needed to cool the facility that will escalate to almost 500 GWh in the time horizon. It is not surprising that Data centers need to come with an associated power plant. This escalating power consumption explains also while many Data Centers are located in proximity of large water sources, like lakes, and in predominantly cold regions.

# 5.2. IOT AND IOE

The IoE has four main components inextricably connected to each other: physical things, data, processes, and people.

1. The Internet of Things (IoT) is the **global network of <u>physical objects</u>** accessed through the Internet and incorporating the infrastructure for the internet-connected world of devices-objects-things. As it was stated before, the IoT is growing into the globally interconnected world where everything is connected. World. The IoE includes the following ITRS 2.0 application areas: mobile products, big data systems, the Cloud 2.0, biomedical products, transportation components and subsystems and interconnect.

2. Data that are generated by all of the devices-objects-things in item 1 above.

3. Smart applications <u>for processing</u> in a timely manner the data generated by the IoT to deliver the right information to the right machine or person at the correct time and thereby for solving problems (societal, economic, environmental, and the like) for industry and governments.

4. Application software/programming interfaces that connect people in more relevant and valuable ways

| Categories  | Year                                                          | 2015 | 2017      | 2019      | 2021      | 2023      | 2025      | 2027      | 2029      |

|-------------|---------------------------------------------------------------|------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|             | Energy source<br>(B = battery; H = energy harvesting)         |      | в         | <b>.</b>  |           | B + H     | B + H     | B+H       | B + H     |

|             |                                                               |      | D         | B + H     | B + H     |           |           |           | в+п       |

|             | Lowest VDD Used By Components (V)                             | 0.8  | 0.75      | 0.7       | 0.65      | 0.65      | 0.55      | 0.45      | 0.45      |

|             | Deep suspend current of MCU (nA)                              | 100  | 72        | 52        | 38        | 27        | 20        | 14        | 10        |

| Power       | Conversion efficiency of DC-to-DC Conversion (%)              | 80%  | 82%       | 86%       | 88%       | 89%       | 91%       | 93%       | 95%       |

|             | Spatial Power Density of DC Converter<br>(W/mm <sup>2</sup> ) | 1    | 1.17      | 1.36      | 1.59      | 1.85      | 2.16      | 2.52      | 2.94      |

|             | Peak Current Consumed by Connectivity<br>Interface (mA)       | 50   | 19.2<br>8 | 7.44      | 2.87      | 1.11      | 0.43      | 0.16      | 0.06      |

|             | Transmission Power per bit (μW/bit)                           | 2.48 | 0.97<br>2 | 0.38<br>1 | 0.14<br>9 | 0.05<br>8 | 0.02<br>3 | 0.00<br>9 | 0.00<br>4 |

| Form factor | Module footprint (mm2)                                        | 500  | 500       | 280       | 179       | 115       | 73        | 47        | 30        |

|             | MCU Number of Cores                                           | 1    | 1         | 1         | 1         | 1         | 1         | 1         | 1         |

|             | MCU Current / Operation frequency (mA/MHz)                    | 30   | 21.7      | 15.7      | 11.3      | 8.9       | 7.7       | 6.7       | 5.8       |